# A 260-340 GHz Dual Chip Frequency Tripler for THz Frequency Multiplier Chains

Alain Maestrini<sup>(1+3),</sup> Charlotte Tripon-Canseliet<sup>(1)</sup>, John S. Ward<sup>(2)</sup>, John J. Gill<sup>(2)</sup> and Imran Mehdi<sup>(2)</sup>

(1) Université Pierre et Marie Curie – Paris 6, LISIF, 4 place Jussieu, case 252, 75252 Paris cedex 5, France Email : alain.maestrini@lisif.jussieu.fr

(2) Jet Propulsion Laboratory, California Institute of Technology, MS 168-314, 4800 Oak Grove Drive, Pasadena, CA 91109, USA

(3) Observatoire de Paris, LERMA, 61 avenue de l'Observatoire, 75014 Paris, France.

Abstract-We designed and fabricated a fix-tuned balanced frequency tripler working in the 260-340 GHz band to be the first stage of a  $\times 3 \times 3 \times 3$  multiplier chain to 2.7 THz. The design of a dual-chip version of this multiplier featuring an input splitter / output combiner as part of the input / output matching networks of both chips - with no degradation of the expected bandwidth and efficiency- will be presented.

#### I. INTRODUCTION

Membrane technology enriched with beam-lead technology has opened new possibilities for frequency multipliers working at terahertz frequencies. The Jet Propulsion Laboratory (JPL) demonstrated in 2004-05 the first fully solid-state frequency tunable source able to pump a Hot Electron Bolometer (HEB) mixer at 1.9 THz [1][2]. Frequency multipliers offer the advantage of working at room temperature and providing 7-15 % of electronically tunable bandwidth in the 1-2 THz region. To go beyond 2 THz, more drive power in the range 800-1200 GHz and subsequently in the range 250-400 GHz is needed. The current work is aimed to create a wideband 300 GHz source to be used as a first stage of a  $\times 3 \times 3 \times 3$  chain to 2.7 THz.

## II. SINGLE AND DUAL CHIP FREQUENCY TRIPLERS

### A. Single chip frequency tripler design and results

The tripler features multiple GaAs Schottky planar anodes in a balanced configuration integrated on a GaAs membrane. This tripler is similar to the 540-640 GHz tripler presented in [3]. The fabrication of the chip and the mechanical blocks was performed at JPL. Preliminary RF tests performed at JPL indicate that the multiplier covers the expected bandwidth and that the efficiency is in the range 1.5-7.5% with 100 mW of input power.

### B. Dual chip frequency tripler design

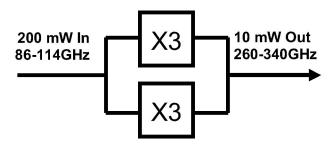

A dual-chip version of the 260-340 GHz tripler was designed using two identical chips to increase power handling capabilities. The output matching circuit of both chips integrates a classic Y-junction that acts as a combiner. Similarly, a Y-junction is used to evenly divide the input power. Fig.1 shows a schematic of this multiplier. Simulations show that the dual-chip tripler should have the same bandwidth than the single-chip tripler with very similar efficiency.

Figure 1. Configuration of the power combined triplers.

#### References

- A. Maestrini, J. Ward, J. Gill, H. Javadi, E. Schlecht, G. Chattopadhyay, F. Maiwald, N.R. Erickson, and I. Mehdi, "A 1.7 to 1.9 THz Local Oscillator Source," *IEEE Microwave and Wireless Components Letters*, Vol. 14, no. 6, pp. 253-255, June 2004.

- [2] A. Maestrini, J. S. Ward, H. Javadi, C. Tripon-Canseliet, J. Gill, G. Chattopadhyay, E. Schlecht, and I. Mehdi, "Local Oscillator Chain for 1.55 to 1.75 THz with 100 μW Peak Power," *IEEE Microwave and Wireless Components Letters*, Vol. 15, no. 12, pp. 871-873, December 2005.

- [3] A. Maestrini, J. Ward, J. Gill, H. Javadi, E. Schlecht, C. Tripon-Canseliet, G. Chattopadhyay and I. Mehdi, "A 540-640 GHz High Efficiency Four Anode Frequency Tripler," *IEEE Trans. Microwave Theory Tech*, Vol. 53, pp. 2835 – 284, September 2005.